DSP

### International Journal of Advances in Telecommunications Electrotechnics, Signals and Systems

a publication of the International Science and Engineering Society

Vol. 2, No. 3 2013

ISSN: 1805-5443

www.ijates.org

# IJInternational Journal ofATAdvances in TelecommunicationsES2Electrotechnics, Signals and Systems

#### a publication of the International Science and Engineering Society

#### Vol. 2, No. 3, 2013

ISSN: 1805-5443

#### Editor-in-Chief

Jaroslav Koton, Brno University of Technology, Czech Republic

#### **Co-Editors**

**Ondrej Krajsa**, Brno University of Technology, Czech Republic **Norbert Herencsar**, Brno University of Technology, Czech Republic **Bilgin Metin**, Bogazicy University, Turkey

#### **Editorial Board**

Oguzhan Cicekoglu, Bogazici University, Turkey Sergey Ryvkin, Trapeznikov Institute of Control Sciences Russian Academy of Sciences, Russian Federation Hongyi Li, Bohai University, China Emilia Daniela Bordencea, TU Cluj-Napoca, Romania Albert Abilov, Izhevsk State Technical University, Russian Federation Joze Guna, University of Ljubljana, Slovenia Jaroslav Koton, Brno University of Technology, Czech Republic Ondrej Krajsa, Brno University of Technology, Czech Republic

#### **Aims and Scope**

The International Journal of Advances in Telecommunications, Electronics, Signals and Systems (IJATES<sup>2</sup>) is an all-electronic international scientific journal with the aim to bring the most recent and unpublished research and development results in the area of electronics to the scientific and technical societies, and is supported by the ISES (International Science and Engineering Society, o.s.). The journal's scope covers all the aspects of telecommunication, signal processing, theory and design of circuits and systems for electronics.

The IJATES<sup>2</sup> is ready to publish experimental and theoretical full papers and letters submitted by prospective authors. Paper submitted for publication must be written in English and must follow a prescribed format. All papers are subjected to a critical peer-review prior to publication.

The IJATES<sup>2</sup> is an open access journal which means that all content is freely available without charge to the user or his/her institution. Users are allowed to read, download, copy, distribute, print, search, or link to the full texts of the articles in this journal without asking prior permission from the publisher or the author. This journal provides immediate open access to its content on the principle that making research freely available to the public supports a greater global exchange of knowledge.

#### www.ijates.org

**Copyright** © 2012-2013, by ISES, o.s. All the copyright of the present journal belongs to the International Science and Engineering Society, o.s.

### CONTENTS

#### Vol. 2, No. 3, 2013

#### ISSN: 1805-5443

| Analysis of Two New Voltage Level Converters With Various Load Conditions<br>Avireni Srinivasulu                                                              | 92  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A hybrid unsupervised and supervised clustering applied to microarray data<br>Raul Malutan, Pedro Gomez Vilda, Monica Borda                                   | 99  |

| Neural Networks Based Physical Cell Identity Assignment for Self Organized 3GPP<br>Long Term Evolution<br>Muhammad Basit Shahab                               | 104 |

| An Overview of Warehouse Optimization<br>Jan Karasek                                                                                                          | 111 |

| A method for automatically constructing the initial contour of the common carotid artery <i>Yara Omran, Kamil Riha</i>                                        | 118 |

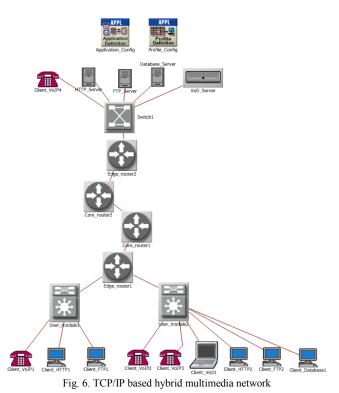

| Analysis of Network Parameters Influencing Performance of Hybrid Multimedia Networks<br>Dominik Kovac, Pavel Masek, Jiří Hošek, Mariya Pavlova, Ondrej Krajsa | 122 |

#### Announcements

| Horizon 2020 Partnership Establishment Workshop in cooperation |      |

|----------------------------------------------------------------|------|

| with Enterprise Europe Network                                 | .129 |

### Analysis of Two New Voltage Level Converters With Various Load Conditions

Mahendranath B and Avireni Srinivasulu, SMIEEE

Abstract—Application of level converter in dual supply voltage circuits is one of the most effective ways to reduce power consumption. To prevent static current, level converter is introduced as an interface at each low-to-high boundary. The design of an efficient level converter with least power consumption and overheads delay is one of the major design constraints. In this paper, two new level converter circuits with low power consumption are proposed for less propagation delay and load adaptability. The proposed level converter circuits are examined using cadence and the design parameters of a 180 nm CMOS process. The simulation results exhibit that proposed level converters can reduce propagation delay and increase speed over the existing circuits available. These level converters are simulated for different loads and operating conditions. The proposed level converters can operate at different values of V<sub>DDL</sub> as +1 V, +1.8 V, +2 V and V<sub>DDH</sub> of +3.3 V. The topology reports low sensitivity and has features suitable for VLSI implementation. The proposed circuits are suited for low power design without degrading performance.

*Keywords*— Dual cascade voltage switch logic, level converter, low power, power dissipation, propagation delay

#### I. INTRODUCTION

At present semiconductor device market demands the manufacture of storage devices having higher operating potentiality, and this triggers another surge in the switching speed. The power consumption has become a major issue on portable electronic systems. As a result, the level converter should have enough current to meet the requirements of transmission speed. This leads to considerable current fluctuations during a short time (di/dt), which may raise switching noises on the power supply lines. In case of large capacitive loads, non-negligible voltage bumps are observed on the power supply lines. These are mainly due to the inductive bond wires, package and board traces, which may induce power supply and ground-bounce (switching noise or Ldi/dt noise). This noise can also lead to data transition delay, oscillation at the end of signal transitions and crosstalk between adjacent signal lines. Moreover, it can even cause malfunctioning of the circuits that are connected to the

Mahendranath. B is with the Department of Electronics & Communication Engineering, Vignan University, Vadlamudi, 522213 Guntur, Andhra Pradesh, INDIA.

Avireni Srinivasulu is with the Department of Electronics & Communication Engineering, Vignan University, Vadlamudi, 522213 Guntur, Andhra Pradesh, INDIA. (Mobile: +91 9502223336; Fax No: +91 863 2534468; e-mail: avireni\_s@yahoo.com (or) avireni@ieee.org).

same supply lines [1].

Due to quadratic relation between voltage and power consumption, reduction in the supply voltage is very effective in decreasing power consumption. However, that would be at the expense of the circuit delay. In order to lower the supply voltage without the degradation of system performance, Clustered Voltage Scaling (CVS) has been developed in which critical and non-critical paths of the circuit are grouped together [2]. In the CVS Scheme, by using low voltage  $(V_{DDL})$  in the non-critical paths and using high supply voltage  $(V_{DDH})$  in speed sensitive paths, the whole system of power consumption could be reduced without degrading the performance. Whenever an output from a low  $V_{\text{DDL}}$  cluster is to drive an input to a high  $V_{\text{DDH}}$ cluster, Level Conversion is required at the interface. The reason being the output from a low swing voltage  $(V_{DDL})$ block cannot connect to a PMOS in a high swing voltage  $(V_{\text{DDH}})$  block directly, since the PMOS cannot shut off with low voltage  $V_{\text{DDL}}$ . One of the main challenges in the CVS Scheme is to design Level Converters (LCs) with less power and overhead delay to interface low voltage  $(V_{DDL})$  blocks with high voltage ( $V_{\text{DDH}}$ ) blocks [3].

Despite the fact that level converter also consumes power, any formal technique that attempts to formulate the use of dual supply voltages for circuit design most possibly take the delay of and the power consumed into account. In other words, the level conversion must be accomplished by minimal delay and lower power consumption to achieve high performance CMOS circuits. Furthermore, a structure such as " $V_{\text{DDL}}$  circuit -  $V_{\text{DDH}}$  circuit -  $V_{\text{DDH}}$  circuit -  $V_{\text{DDH}}$ circuit..." need a lot of level converters to be inserted at each " $V_{DDL}$  circuit -  $V_{DDH}$  circuit" interface [4]. Hence both lowering the power consumed in the level converter and reducing the number of level converters as such becomes an important issue for the use of dual supply voltages. Care has been taken to design level converter accurately for lowering power consumption and propagation delay without degrading performance. In a traditional Dual Cascade Voltage Switching (DCVS), large delay has been resulted because of the contentions problem between different transistors on the level shifting path. This contention problem will lead to increase both in delay time and power consumption [5-13]. For practical purposes, a CMOS logic circuit with mixed gates operating on a lower supply voltage V<sub>DDL</sub> and on a higher supply voltage V<sub>DDH</sub> may be preferred. However, any gate operating on V<sub>DDH</sub> and connected after the gate operating on  $V_{DDL}$  generates a short-circuit current.

Manuscript received February 28, 2013, revised July 26, 2013.

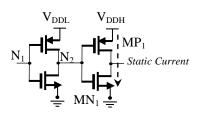

Fig. 1 Direct connection of  $V_{DDL}$  circuit and the  $V_{DDH}$  circuit

Figure.1 shows a CMOS logic circuit taking into consideration the output of first CMOS inverter is directly connected to the second CMOS inverter. The first CMOS inverter operates on lower supply voltage  $V_{\rm DDL}$  and the second one on a higher supply voltage  $V_{\text{DDH.}}$  If the input node  $N_1$  of  $V_{DDL}$  circuit swings from high to low, the output node  $N_2$  retains the reverse that is  $V_{DDL}$ . Subsequently, the logical high at node N<sub>2</sub> should turn off the pull-up transistor MP<sub>1</sub> and turn on the pull-down transistor MN<sub>1</sub>. Although the voltage at node N2 is high enough to activate the NMOS transistor MN<sub>1</sub>, it cannot turn off the PMOS transistor MP<sub>1</sub> due to the fact that  $V_{\text{DDL}} < V_{\text{DDH}} - |V_{\text{th,P}}|$ . Therefore, there exist a static current flowing directly from the applied voltage source to ground through the path of  $MP_1$  and  $MN_1$ . This static current also consumes power which is not desirable for low power application [6]. To restrict this unwanted power consumption, there should be a level converter circuit placed between  $V_{DDL}$  and  $V_{DDH}$  circuits. The main advantage of the level converter circuit is to reduce the static power consumption. Level converter transforms a logical high produced by a  $V_{DDL}$  circuit to the logical high for a V<sub>DDH</sub> circuit. Thus, the condition of both networks MP1 and MN1 are activated at a time as described in Fig. 1 would not be possible, and the power consumption by the static current therefore gets eliminated. In order to achieve high performance CMOS circuits, the level converter circuit must be designed so as to have minimal delay and power consumption.

#### II. THE CONVENTIONAL LEVEL CONVERTERS

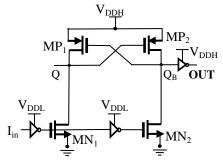

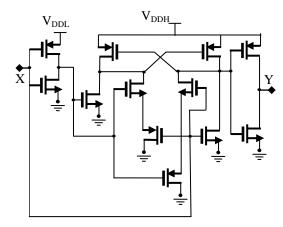

The circuit diagram of conventional level converter is shown in Fig. 2. It is termed as Dual Cascade Voltage Switch (DCVS), interposed between gates operating on different supply voltages in a CMOS logic circuit, to prevent the short-circuit current and reduce power consumption. In this circuit there exists two cross coupled PMOS transistors MP<sub>1</sub> and MP<sub>2</sub> to generate the circuit load. The cross coupled PMOS transistor acts as a differential pair. As the output at one side gets pulled down, followed by opposite PMOS transistor to turn ON, and the output on that side will be plugged high. Below the PMOS load, there are two NMOS transistors MN<sub>1</sub> and MN<sub>2</sub> that are regulated by the input signal [7].

Although the level converter blocks the short circuit current, it consumes relatively large dynamic power while carrying out switching operation. If the CMOS logic circuit must have many level converters; the power consumption therefore would have increased to nullify the effort of decreasing the power consumption by using the two supply voltages  $V_{DDL}$  and  $V_{DDH}$ . Furthermore, this conventional level converter has relatively large delay as it has to rely on a contention between different transistors on the level

conversion [7].

Fig. 2 Conventional level converter (DCVS)

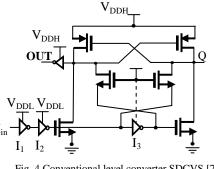

Figure 3 shows the conventional level converter [6], with 12 transistors. This circuit has large power dissipation and propagation delay because it contains more number of transistors.

Fig. 3 Conventional level converter [6]

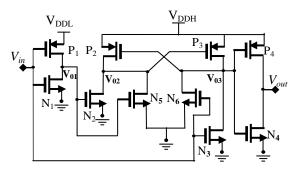

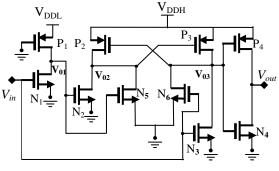

Figure. 4 shows the conventional level converter Standard Dual Cascade Voltage Switch (SDCVS) [7] which endorse the same cross coupled pair of PMOS transistors as DCVS with 14 transistors. The simulation profile of Fig. 4 has indicated the results in the higher propagation delay and power dissipation. To overcome these disadvantages, two new level converters with 10 transistors are proposed in this paper. These proposed circuits reduce the propagation delay and are shown in Fig. 5 and Fig. 6.

Fig. 4 Conventional level converter SDCVS [7]

The remaining sections of the paper are structured as follows. The new proposed level converter and circuit description is presented in section III. Simulation results and comparative conventional circuits are included in section IV. Finally, conclusion is included in section V.

#### III. PROPOSED LEVEL CONVERTERS

The proposed level converters are shown in Fig. 5 and Fig. 6. In these circuits, the level conversion circuit converts a signal  $V_{in}$  on the lower voltage side to a signal  $V_{out}$  on the higher supply voltage side; the signal  $V_{in}$  is transmitted to the inverted phase, which inturn generated by inverter constituted by transistors P<sub>1</sub> and N<sub>1</sub>, ultimately transmitted to the gates of transistors N<sub>2</sub> and N<sub>4</sub>. The respective gates of transistors P<sub>3</sub> and P<sub>2</sub>, while the source of both transistors are connected to the higher supply voltage V<sub>DDH</sub> and V<sub>03</sub> is again connected to the gate terminals of P<sub>4</sub> and N<sub>4</sub> in the output stage, which is further connected to the higher supply voltage V<sub>DDH</sub>. Here in this circuit the  $V_{in}$  signal is given as 0/1-V, 0/1.8-V and 0/2-V voltage levels and V<sub>DDH</sub> is 0/3.3-V voltage level.

Fig. 5 Proposed level converter-1

The proposed level converter-1 is shown in Fig. 5, composed of inverter, DCVS logic and an output stage. It converts 0/1-V, 0/1.8-V and 0/2-V voltage swing to 0/3.3-V voltage swing. To reduce the body effect in Fig. 5, the bulk of the PMOS and NMOS transistors are connected to their source and drain terminals respectively. The proposed level converter employs the same cross-coupled pair of PMOS transistors as DCVS. Two NMOS transistors N<sub>5</sub> and N<sub>6</sub> are added to achieve high speed operation. These two transistors are connected to the gate terminals of P<sub>2</sub> and P<sub>3</sub> transistors to increase the switching speed of the output transition. In Fig. 5, P<sub>1</sub> and N<sub>1</sub> transistors acts as input inverter with low supply voltage level V<sub>DDL</sub>. The output stage consists of PMOS P<sub>4</sub> and NMOS N<sub>4</sub>. The node voltage V<sub>03</sub> is connected to the gate terminal of transistor P<sub>4</sub> and N<sub>4</sub>.

The circuit operates as follows: when the voltage level of input signal swings from high to low, the output voltage level of input inverter becomes the lower supply voltage V<sub>DDL</sub>. Therefore, N<sub>2</sub> and N<sub>5</sub> transistors are turned ON; as a result, node  $V_{02}$  is then discharged to ground. Thus,  $P_3$  is turned ON and then voltage level of node  $V_{03}$  becomes a higher supply voltage  $V_{DDH}$ . In this case,  $P_2$ ,  $N_3$  and  $N_6$ transistors are turned OFF, and there by it has been made possible to prevent a short-circuit current from flowing between the higher supply voltage V<sub>DDH</sub> and the ground. When the voltage level of the input signal is switched to logic high, the output voltage level of the input inverter becomes logic low. Therefore, N<sub>3</sub> and N<sub>6</sub> transistors are turned ON; as a result node  $V_{03}$  is then discharged to ground. In this case, transistor  $P_2$  is turned ON and thereby, transistor P<sub>3</sub> turns OFF. There by transistors N<sub>2</sub> and N<sub>5</sub> are also turned OFF and made it possible to prevent a short-circuit current from flowing between the higher power supply voltage  $V_{DDH}$

Fig. 6 Proposed level converter-2

and ground. It is thus clear that the output level transition in each input signal condition switches fast. These results contribute to faster output transition as well as contention problem on nodes  $V_{02}$  and  $V_{03}$ . As a result of this propagation delay time of the circuit gets reduced.

Figure 6 display the proposed level converter-2 which is composed of pseudo inverter, DCVS logic and an output stage. It converts 0/1-V, 0/1.8-V and 0/2-V voltage swing to 0/3.3-V voltage swing. To reduce the body effect in Fig. 6 too the bulk of the PMOS and NMOS transistors are connected to their respective source and drain terminals. The proposed level converter employs the same cross-coupled pair of PMOS transistors as DCVS. Two NMOS transistors N<sub>5</sub> and N<sub>6</sub> are introduced to achieve high speed operation. These two transistors are connected to the gate terminals of  $P_2$  and  $P_3$  transistors to increase the switching speed of the output transition. In Fig. 6, transistor P<sub>1</sub> and N<sub>1</sub> transistor acts as input pseudo inverter with low supply voltage level  $V_{DDL}$ . The output stage consists of PMOS  $P_4$  and NMOS  $N_4$ . The node voltage  $V_{03}$  is connected to the gate terminal of transistor P<sub>4</sub> and N<sub>4</sub>.

Nextly, operation of the proposed level converter-2 is explained as follows. While the gate of PMOS P1 transistor is connected to ground it will always be in ON condition. While the voltage level of input signal swings from low to high, the NMOS transistor N1 turns ON and the voltage at node  $V_{01}$  is discharged to ground, so that the output voltage level of input inverter becomes low. Therefore, transistor N<sub>3</sub> and  $N_6$  transistors are turned ON; as a result, node  $V_{02}$  is converted for supply of high voltage  $V_{\text{DDH}}$ . Thus,  $P_2$  is turned ON and then voltage level of node  $V_{03}$  becomes a low. In this case, transistors P3, N2 and N5 are turned OFF, and there by it is made possible to prevent a short-circuit current from flowing between the higher supply voltage  $V_{\text{DDH}}$  and the ground. When the voltage level of the input signal is switched to logic low, the output voltage level of the input inverter attains lower supply voltage V<sub>DDL</sub>. Therefore, N<sub>2</sub> and N<sub>5</sub> transistors are turned ON; as a result node  $V_{03}$  then becomes higher supply voltage  $V_{DDH}$ . In this case, transistor P<sub>3</sub> is turned ON, and thereby, transistor P<sub>2</sub> to OFF. Moreover, transistors N<sub>3</sub> and N<sub>6</sub> are also turned OFF, and thereby, it is made possible to prevent a short-circuit current from flowing between the higher power supply voltage V<sub>DDH</sub> and ground. It is thus clear that the output level transition in each input signal condition switches fast. These results provide faster output transition as well as contention into problems thrusting on nodes  $V_{02}$  and  $V_{03}$ . Consequently propagation delay time of the circuit becomes lesser than proposed level converter-1, with no short-circuit current flow; therefore it is possible to reduce the power dissipation.

#### IV. SIMULATION RESULTS

The circuit in Fig. 5, Fig. 6 and low power level converter [6] and SDCVS [7] were simulated by using cadence and the model parameters of a 180 nm CMOS process. The simulations were carried out with pulse amplitude of +1 V, +1.8 V, +2 V and frequency of 1 MHz.

In order to observe the performance of the proposed level converters under various load conditions, the conventional and proposed circuits are simulated at load capacitance varying from 1 pF to 15 pF for +1 V input voltage and 1 pF to 25 pF for +1.8 V input voltage. Standard DCVS level converter in Fig. 2 suffers from the contention problem; therefore simulation results show maximum power and delay over head. On the other hand low power level converter [6] and standard SDCVS [7] level converter uses more transistors in its operation as compared to proposed level converters, that results in increase in power consumption and propagation delay.

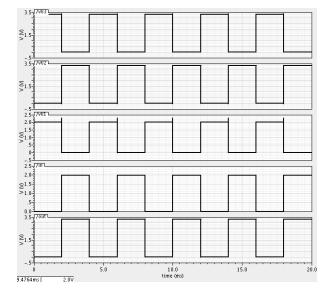

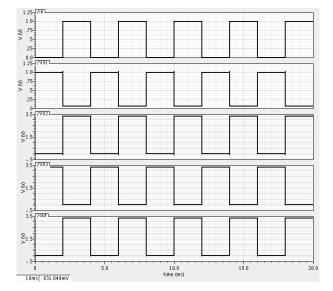

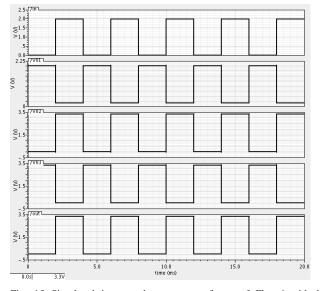

The typical simulated input and output waveforms on the configuration of Fig. 5, with  $V_{DDL} = +1V$ , +1.8V, +2V,  $V_{DDH} = +3.3V$  and output load of  $C_L = 10$  pF is presented in Fig. 7, 8, 10 respectively. It is evident from Fig. 7 simulated input and output waveforms are with amplitude of +1 V and +3.3V respectively with no voltage drop. For all the level converters the supply rail  $V_{DDL}$  of +1 V, +1.8V, +2 V,  $V_{DDH}$  of 3.3V and pulse input parameters shown in Table. I was used.

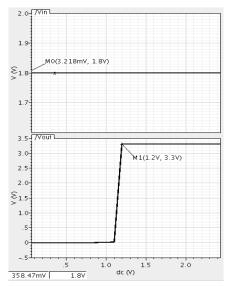

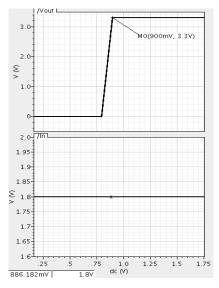

Figure 9 shows the simulated DC Response of proposed voltage level convrter-1 of Fig. 5. From Fig. 9 it is evident that the output voltage is varied with respect to input voltage.

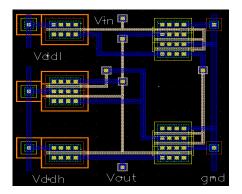

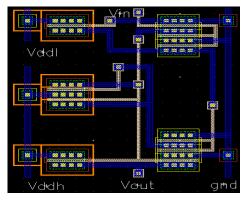

The layout of the proposed voltage level converter-1 of

| TABLE I – PULSE INPUT PARAMETERS |                   |  |  |  |  |  |

|----------------------------------|-------------------|--|--|--|--|--|

| Voltage 1                        | +1 V, +1.8 V, +2V |  |  |  |  |  |

| Voltage 2                        | 0 V               |  |  |  |  |  |

| Delay Time                       | 1 ps              |  |  |  |  |  |

| Rise Time                        | 2 ps              |  |  |  |  |  |

| Fall Time                        | 1 fs              |  |  |  |  |  |

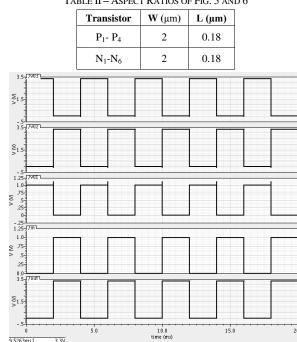

TABLE II – ASPECT RATIOS OF FIG. 5 AND 6

Fig. 7 Simulated input and output waveforms of Fig. 5 with load capacitance  $C_L$ =5 pF (Supply rail voltages  $V_{DDH}$ = +3.3V and  $V_{DDL}$ =1 V).

Fig. 5 has been designed using Assura layout XL with 180 nm technology file. Layout of proposed voltage level converter-1 of Fig. 5 is shown in Fig 11. The area of the proposed voltage level converter-1 is 164.64  $\mu$ m<sup>2</sup>.

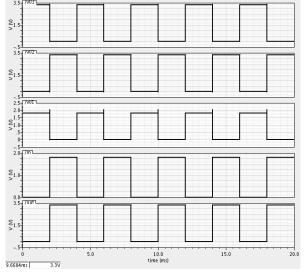

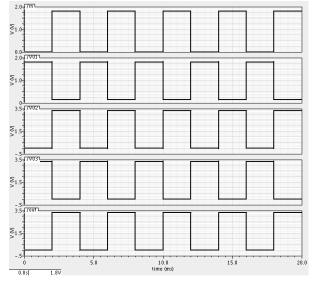

Fig. 12, 13, 15 shows the simulated waveforms on nodes  $V_{in}$ ,  $V_{01}$ ,  $V_{02}$ ,  $V_{03}$  and  $V_{out}$  of the proposed level converter-2 with  $V_{DDL} = +1V$ , +1.8V, +2V,  $V_{DDH} = +3.3V$  and output load of  $C_L = 10$  pF respectively. It is evident from Fig. 10 simulated input and output waveforms are with amplitude of +1 V and +3.3V respectively without any voltage drop. For all the level converters the supply rail  $V_{DDL}$  of +1 V, +1.8V, +2 V,  $V_{DDH}$  of +3.3V and pulse input parameters shown in Table. I was used. The aspect ratios of Fig. 5 and 6 transistors are given in table II.

Figure 14 shows the simulated DC Response of proposed voltage level convrter-2 of Fig. 6. From Fig. 14, it is evident that the output voltage is varied with respect to input voltage.

The layout of the proposed voltage level converter-2 of Fig. 6 has been designed using Assura layout XL with 180 nm technology file. Layout of proposed voltage level converter-2 of Fig. 6 is shown in Fig 16. The area of the proposed voltage level converter-1 is 170.79  $\mu$ m<sup>2</sup>.

Fig. 8 Simulated input and output waveforms of Fig. 5 with load capacitance  $C_L$ = 10 pF (Supply rail voltages  $V_{DDH}$ =3.3V and  $V_{DDL}$ =1.8 V).

Fig. 9 Simulated DC response of Fig. 5 with load capacitance  $C_L{=}$  10 pF (Supply rail voltages  $V_{DDH}{=}$  +3.3V and  $V_{DDL}{=}$  +1.8 V).

Fig. 10 Simulated input and output waveforms of Fig. 5 with load capacitance  $C_L$ = 20 pF (Supply rail voltages  $V_{DDH}$ =3.3V and  $V_{DDL}$ =2 V).

Fig. 11 Layout of proposed Fig 5

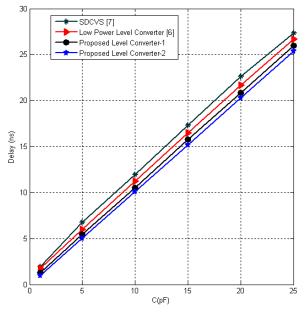

Figure 17 empowers the comparison of propagation delay for proposed level converters, low power level converter [6] and conventional SDCVS [7]. In Fig. 17 load capacitance is varied from 1 pF to 25 pF with input pulse amplitude of +1.8 V and frequency of 1 MHz. It is thus clear that the proposed level converters have less propagation delay and load adaptability than the earlier ones. From the simulation results, it is proved that the delay and power consumption in proposed level converters is very less as compared to that of in the standard DCVS, SDCVS and low power level converters. It is also observed that falling delay and rising delay in case of proposed level converter is much less as compared to the existing circuits. Accordingly, the proposed level converter circuits can be effectively applied to LSI high speed input-output circuit, as an interface between internal and external buses such as a server or exchanger, and as an interface circuit between optical devices for optical communication and an LSI, etc.

Table III represents the comparative study of propagation delay for the proposed level converters, low power level converter [6] and conventional SDCVS [7]. In Table II load capacitance is varied from 1 pF to 15 pF with input pulse amplitude of +1 V and frequency of 1MHz. From Table II also it is clear that there is a significant reduction of delay in the proposed level converter compared to the existing circuits.

Table IV shows the simulated values of the propagation delay for the proposed level converter-1 for different supply

Fig. 12 Simulated input and output waveforms of Fig. 6 with load capacitance  $C_L$ = 5 pF (Supply rail voltages  $V_{DDH}$ = +3.3V and  $V_{DDL}$  = 1 V).

Fig. 13 Simulated input and output waveforms of Fig. 6 with load capacitance  $C_L=5 \text{ pF}$  (Supply rail voltages  $V_{DDH}=3.3 \text{ V}$  and  $V_{DDL}=1.8 \text{ V}$ ).

Fig. 14 Simulated DC response of Fig. 6 with load capacitance  $C_L{=}$  10 pF (Supply rail voltages  $V_{DDH}{=}$  +3.3V and  $V_{DDL}{=}$  +1.8 V).

voltages  $V_{DDL}$  of (+1 V, +1.2 V, +1.8 V, and +2 V) and  $V_{DDH}$  of (+3.3 V, +5 V) with load capacitor  $C_L$  ranging from

Fig. 15 Simulated input and output waveforms of Fig. 6 with load capacitance  $C_L=5 \text{ pF}$  (supply rail voltages  $V_{DDH}=+3.3 \text{V}$  and  $V_{DDL}=+2 \text{ V}$ ).

Fig. 16 Layout of proposed Fig 6

from 1 pF to 10 pF. It is also doubly clear that proposed level converters gives less propagation delay for low voltage and high voltage conversion and hence the proposed converter is very useful for low voltage and high voltage application such as PCI-X Interface.

Table V shows the simulated values of the propagation delay for the proposed level converter-2 for different supply voltages  $V_{DDL}$  of (+1 V, +1.2 V, +1.8 V and +2 V) and  $V_{DDH}$  of (+3.3 V, +5 V) with load capacitor  $C_L$  ranging from 1 pF to 10 pF. It is therefore clear that proposed level converter-2 of Fig. 6 gives less propagation delay for low voltage and high voltage conversion compared to proposed level converter-1 of Fig. 5 and hence the former is stated to have an edge over the later in efficiency and performance as well.

#### V. CONCLUSION

Two new level converters have been tested and designed with 180 nm CMOS Technology with  $V_{DDL} = +1$  V, +1.8 V, +2 V and  $V_{\text{DDH}}$  = 3.3 V. It has resulted into minimizing the propagation delay and switching noise. The proposed level converters therefore can reduce the contention problem that existed in the conventional DCVS circuit. Also there is a reduction in the rising time and falling time in the proposed level converters when compared to conventional designs. Simulation results however show that the proposed designs have recorded less noise and less propagation delay, compared to previous designs. The topology reports low sensitivity and has features suitable for VLSI

Fig. 17 Proposed level converters and conventional level converters propagation delay comparison for different loading conditions with  $V_{DDL}$  = +1.8V and  $V_{DDH}$  = +3.3 V.

implementation.

#### REFERENCES

- Y.Lin, Xuecheng Zou, Zhaoxiao Zheng, W. Huo, Xiaofei Chen and W. Kang, "High-speed, Low Switching Noise and Load Adaptive Output Buffer" *in Proc. the Int.Symp. Integrated circuits 2009*, (ISCI 2009), Singapore, 14-16 Dec, 2009, pp. 280-282.

- [2] M. Hamada, M. Takahashi, H. Arakida, A. Chiba, T. Terazawa, T. Ishikawa, M. Kanazawa, M. Igarashi, K. Usami, and T. Kuroda, "A top-down low power design technique using clustered voltage scaling with variable supply-voltage scheme," *in Proc. the IEEE Custom Integrated Circuits Conf.*, 1998, pp. 495–498.

- [3] L. Benini, E. Macii, and G. De Micheli, "Designing low power circuits: Practical recipes," *IEEE Circuit Syst. Mag.*, vol. 1, no. 1, pp. 6–25, 2001.

- [4] J. Y. Jou, and D. S. Chou, "Sensitisable-path-oriented clustered voltage scaling technique for low power," *in Proc. the IEEE* on *Comput. Digit. Tech.*, vol. 145, no. 4, Jul 1998, pp. 301-307.

- [5] J. S. Shor, Y. Afek, and E. Engel, "IO buffer for high performance, low-power application," in Proc. the IEEE Custom Integrated Circuits Conf., 1997, pp. 595-598.

- [6] Chin Ping-Yuan, Yu Chien-Cheng "A voltage Level Converter Circuit Design with Low Power Consumption" in Proc. the IEEE International Conference on ASIC, Oct. 22-27, 2005, Shanghi, pp. 358-359.

- [7] Chien-Cheng Yu, Wei-Ping Wang and Bin-Da Liu "A new level converter for low power applications" in Proc. the IEEE International Symposium on Circuits syst., 2001, vol.1, pp. 113-116.

- [8] Mahendranath. B and Avireni Srinivasulu, "Performance analysis of a new CMOS output buffer", in proc. the IEEE International Conference on Circuit, Power and Computing Technologies (IEEE ICCPCT-2013), Kumaracoil, India, Mar 21-22, 2013, pp. 752-755. DOI: 10.1109/ICCPCT.2013.6529041.

- [9] T. Venkata Rao and Avireni Srinivasulu, "Modified level restorers using current sink and current source inverter structures for BBL-PT full adder", *Radioengineering*, vol. 21, no. 4, pp. 1279-1286, Dec 2012. ISSN: 1210-2512.

- [10] Shih-Lun Chen, Ming-Dou ker "An Output Buffer for 3.3 V application in a 0.13 μm 1/2.5-V CMOS Process" *IEEE transaction* on circuits and systems –II: express briefs, vol. 54, pp. 14-18, Jan 2007.

- [11] R. J. Baker, H. W. Li, and D. E. Boyce, "CMOS Circuit Design, Layout, and Simulation", New York: IEEE Press, 1997.

- [12] Avireni Srinivasulu and Madugula Rajesh, "ULPD and CPTL Pull-Up Stages for Differential Cascode Voltage Switch Logic," *Journal of Engineering (Hindawi)*, vol. 2013, Article ID 595296, 5 pages, 2013. DOI: 10.1155/2013/595296 ISSN: 2314-4912.

[13] I. Kavitha Madhuri, Avireni Srinivasulu, P. Chandra Shaker and Indira Priyadarsini. S, "Two CMOS Schmitt trigger circuits using current sink and pseudo inverters", *International Journal of Computer Applications*, iC3S - Number 3, Year of Publication: 2013, pp. 18-21. ISSN: 0975 – 8887.

Mahendranath Bheemanboina was born in Tharlupadu, Prakasam District, (A.P), India in 1989. He received the B.Tech degree in electronics and communication engineering from J.N.T.University, Kakinada in 2010. Currently, he is working towards his M.Tech thesis under the esteemed guidance of Dr. Avireni Srinivasulu. His area of research includes VLSI Design.

Avireni Srinivasulu was born in Thurimella, Andhra Pradesh, India. He received the B.Tech degree in electronics and communication engineering from Sri Venkateswara University, Tirupati in 1986, M.E, degree in power electronics engineering from Gulbarga University, Gulbarga in 1991, M.S, degree in software systems from Birla Institute of Technology and Science (BITS), Pilani in 1998 and Ph.D, degree in electronics and communication engineering (VLSI Design) from Birla Institute of Technology, Mesra, India in 2010.

He worked as a Lecturer, Assistant Professor, Reader and Associate Professor in the Department of Electronics and Communication Engineering, T.G.L.G. Polytechnic, Adoni; Guru Nanak Dev Polytechnic, Bidar; K.S.R.M. College of Engineering, Kadapa; Defence University Engineering College, Debre-Zeit, Ethiopia; Kigali Institute of Science, Technology & Management, Kigali, Rwanda; Birla Institute of Technology, Mesra, Ranchi and working as a Professor in the Department of Electronics and Communication Engineering, Vignan University, Vadlamudi, Guntur, India. He has 25 years of teaching and 15 years of research experience in the Department of Electronics and Communication Engineering.

Dr. Avireni.S is a senior member of IEEE, senior member of IACSIT, life member of I.S.T.E and a member of the Institution of Engineers (India). He has published over 30 articles in international journals and international conference proceedings; his main research areas are microelectronics, VLSI design and analog ASIC.

#### TABLE. III COMPARISON OF PROPAGATION DELAY FOR FIG. 5 FIG. 6 AND CONVENTIONAL LEVEL CONVERTERS FOR DIFFERENT LOAD CONDITIONS

| Level<br>Converters | Supply Rail<br>Voltages |            |                      | Propagati            | on Delay (ns)         |                        |

|---------------------|-------------------------|------------|----------------------|----------------------|-----------------------|------------------------|

|                     | $+V_{DDL}$              | $+V_{DDH}$ | $C_L\!\!=\!\!1 \ pF$ | $C_L\!\!=\!\!5 \ pF$ | C <sub>L</sub> =10 pF | $C_L\!\!=\!\!15 \; pF$ |

| SDCVS [7]           | 1 V                     | 3.3 V      | 4.553                | 9.767                | 15.04                 | 19.68                  |

| LPLC [6]            | 1 V                     | 3.3 V      | 4.627                | 8.631                | 14.3                  | 15.9                   |

| Proposed Fig.5      | 1 V                     | 3.3 V      | 4.868                | 8.376                | 13.28                 | 16.54                  |

| Proposed Fig.6      | 1 V                     | 3.3 V      | 2.998                | 7.169                | 12.41                 | 15.13                  |

TABLE. IV COMPARISON OF PROPAGATION DELAY FOR FIG. 5 WITH DIFFERENT LOAD CONDITIONS AND SUPPLY RAIL VOLTAGES

|                              | y Rail<br>ages               | -                 | $\begin{array}{c c} Capacitor \ Output \ load \\ (C_L = 1 \ pF) \end{array} \begin{array}{c} Capacitor \ Output \ load \\ (C_L = 5 \ pF) \end{array} \begin{array}{c} Capacitor \ Output \ load \\ (C_L = 10 \ pF) \end{array}$ |               | 1 1               |                |               | oad               |                   |               |

|------------------------------|------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|----------------|---------------|-------------------|-------------------|---------------|

| +V <sub>DDL</sub><br>(Volts) | +V <sub>DDH</sub><br>(Volts) | Rise Time<br>(fs) | Fall Time<br>(ps)                                                                                                                                                                                                               | Delay<br>(ns) | Rise Time<br>(ps) | Fall Time (ns) | Delay<br>(ns) | Rise Time<br>(ps) | Fall Time<br>(ns) | Delay<br>(ns) |

| 1                            | 3.3                          | 7.93              | 515.6                                                                                                                                                                                                                           | 4.187         | 45.85             | 2.532          | 8.376         | 4.209             | 5.057             | 13.61         |

| 1.2                          | 3.3                          | 4.44              | 510                                                                                                                                                                                                                             | 2.404         | 66.29             | 2.53           | 6.59          | 5.162             | 5.063             | 11.82         |

| 1.8                          | 3.3                          | 37.54             | 509.3                                                                                                                                                                                                                           | 1.462         | 101               | 2.535          | 5.677         | 1.055             | 5.078             | 10.9          |

| 1.2                          | 5                            | 22.61             | 690.6                                                                                                                                                                                                                           | 2.487         | 618               | 3.397          | 7.152         | 1.241             | 6.861             | 13.09         |

| 1.8                          | 5                            | 55.27             | 683.8                                                                                                                                                                                                                           | 1.457         | 936.3             | 3.402          | 6.139         | 498.9             | 6.85              | 11.89         |

| 2                            | 5                            | 960.8             | 682.9                                                                                                                                                                                                                           | 1.546         | 618               | 3.397          | 7.152         | 1.241             | 6.861             | 13.09         |

TABLE. V COMPARISON OF PROPAGATION DELAY FOR FIG. 6 WITH DIFFERENT LOAD CONDITIONS AND SUPPLY RAIL VOLTAGES

|                              | Supply Rail<br>Voltages      |                   | Capacitor Output load<br>(C <sub>L</sub> = 1 pF) |               |                   | itor Output lo<br>C <sub>L</sub> = 5 pF) | oad           | -                 | itor Output lo<br>C <sub>L</sub> = 10 pF) | oad           |

|------------------------------|------------------------------|-------------------|--------------------------------------------------|---------------|-------------------|------------------------------------------|---------------|-------------------|-------------------------------------------|---------------|

| +V <sub>DDL</sub><br>(Volts) | +V <sub>DDH</sub><br>(Volts) | Rise Time<br>(ps) | Fall Time<br>(ps)                                | Delay<br>(ns) | Rise Time<br>(ps) | Fall Time<br>(ns)                        | Delay<br>(ns) | Rise Time<br>(ps) | Fall Time<br>(ns)                         | Delay<br>(ns) |

| 1                            | 3.3                          | 496               | 516.4                                            | 2.998         | 26.42             | 2.534                                    | 7.169         | 6.521             | 5.706                                     | 12.41         |

| 1.2                          | 3.3                          | 4.332             | 509.9                                            | 1.622         | 574.3             | 2.532                                    | 5.82          | 2.348             | 5.05                                      | 11.10         |

| 1.8                          | 3.3                          | 1.134             | 520.7                                            | 1.112         | 719.2             | 2.534                                    | 5.134         | 7.194             | 5.057                                     | 10.56         |

| 1.2                          | 5                            | 53.15             | 690.5                                            | 1.709         | 570.1             | 3.404                                    | 6.382         | 1.816             | 6.865                                     | 12.3          |

| 1.8                          | 5                            | 665               | 691.2                                            | 1.226         | 613.6             | 3.445                                    | 5.94          | 693.2             | 6.803                                     | 11.74         |

| 2                            | 5                            | 710.3             | 696.1                                            | 1.148         | 14.43             | 3.409                                    | 5.837         | 15.89             | 6.868                                     | 11.75         |

### A hybrid unsupervised and supervised clustering applied to microarray data

Raul Măluțan, Pedro Gómez Vilda, Monica Borda

*Abstract*— Clustering methods have been often applied to large data with the main purpose of reducing the dimension, time computation and identifying clusters with similar behavior. This work presents a state-of-the-art in unsupervised clustering and cluster validation. It proposes a method for hybrid bi-clustering of microarray data combined with a supervised validation for determining the optimal amount of clusters of genes.

*Keywords* — microarray, clustering, internal validation, external validation, gene shaving.

#### I. INTRODUCTION

The microarray data processing challenges nowadays consists of how to make it more reliable, easy to use and efficient. In this task other fields of knowledge as Signal and Image Processing, Pattern Recognition, or Statistical Data Analysis [1] may help in yielding their enormous potential in solving problems as microarray image enhancement, segmentation, correction, gridding, data analysis, reliable expression estimation in relation with hybridization dynamics, etc. Others have to see with data interpretation, dimensionality reduction, cluster analysis, etc.

Clustering techniques play an important role in analyzing high dimensional data such as microarray data. An analysis of microarray data is a search for genes that have similar, correlated patterns of expression. This indicates that some of the data might contain redundant information. For example, if a group of experiments were more closely related than it was expected, some of the redundant experiments can be ignored, or use some average of the information without loss of information.

Data analysis methods [2] can be grouped in two categories: supervised and unsupervised. In the

Manuscript received Ortober 28, 2012, revised March 04, 2013. This work was supported by the project "Development and support of multidisciplinary postdoctoral programmes in major technical areas of national strategy of Research - Development - Innovation" 4D-POSTDOC, contract no. POSDRU/89/1.5/S/52603, project co-funded by the European Social Fund through Sectoral Operational Programme Human Resources Development 2007-2013.

R. Malutan is with the Communications Department, Technical University of Cluj-Napoca, 26-28 George Baritiu St., 400027 Cluj-Napoca, Romania, (phone: 004-0264-401564; fax: 004-264-401575; e-mail: raul.malutan@com.utcluj.ro).

P. Gómez Vilda is with Departamento de Arquitectura y Tecnología de Sistemas Informáticos (DATSI), Universidad Politécnica de Madrid, Campus de Montegancedo, s/n, 28660, Boadilla del Monte, Madrid, Spain (e-mail: pedro@pino.datsi.fi.upm.es).

M. Borda is with the Communications Department, Technical University of Cluj-Napoca, 26-28 George Baritiu St., 400027 Cluj-Napoca, Romania (e-mail: Monica.Borda@com.utcluj.ro).

doi: 10.11601/ijates.v2i3.21

unsupervised approach, also known as clustering, data is organized without a priori information.

This paper describes several unsupervised algorithms used mostly for microarray data, like k-means, Partitioning Around Medoids (PAM) and Expectation-Maximization (EM). These algorithms have proven to be a useful when the number of clusters is known or can be estimated. Two of them, k-means and PAM, are based on minimizing the mean squared error, while the third, EM, on mixture modeling.

The algorithms were run on several data sets [3], observing that the quality of the obtained clusters is dependent on the number of clusters specified. To assess the effectiveness of these algorithms, but also to estimate the actual number of clusters, several clustering validation method were implemented. These methods consist in calculating internal and external indices used to estimate the optimal number of clusters for each algorithm.

The microarray data has a particularity compared with other type of data. A two dimension data is in fact a gene expression matrix which usually has the rows corresponding to genes from an experiment and the columns corresponding to different experiments. If one finds that two rows are similar, it can be assumed that the genes corresponding to the rows are co-regulated and functionally related, and by comparing two columns it can found which genes are differentially expressed in each experiment. To perform a comparison a similarity measure between the objects, genes or experiments under comparison, has to be used. Mostly the same algorithm is used for analyzing both the genes and the experiments, *i.e.* bi-clustering of microarray data.

Considering the dimensionality of the data, large amount of genes and small number of experiments, we propose in this paper a hybrid bi-clustering, where we combine unsupervised methods with the purpose of obtaining the optimal combination of clusters.

Besides, as a supplementary validation, a supervised method was used on the same data. Supervised classification represents the issue of identifying the subset to which new observations belong, where the identity of the subset is unknown, on the basis of a training set of data containing observations whose subset is known. Therefore the classification will display a variable behavior which can be analyzed by statistics. It is required for new sample items to be placed into the respective groups based on quantitative information on one or more measurements, attributes or features and based on the training set in which previously decided groupings are already established.

#### II. CLUSTER ANALYSIS

#### A. Unsupervised algorithms

The unsupervised clustering methods are divided in two categories: hierarchical and non-hierarchical. Hierarchical methods group the objects in an iterative way, generating a hierarchical tree structure, also known as dendogram. On the other hand, the non-hierarchical clustering, or partitioning methods, does the partitioning of a data set into a predefined number of different clusters, without a hierarchical structure. Beside, these algorithms produce an integer number of partitions, and also they optimize a certain criterion function. The partitioning methods classify the data in k clusters which must fulfill the following conditions:

- each group should contain at least one element;

- each object must belong to one group only.

For the microarray data the most suitable clustering methods are unsupervised ones, because we cannot observe the (real) number of clusters in the data [4]. From the unsupervised algorithms used in microarray data analysis the k-means, PAM (Partitioning Around Medoids) and EM (Expectation Maximization) are the most frequently used. The first two from the list are using the minimization of the root mean square error and the third one is using the mixing models methods.

The PAM algorithm [2] is based on the search for k representative objects or medoids among the objects of the dataset. These objects should represent the structure of the data. After finding a set of k medoids, k clusters are constructed by assigning each object to the nearest medoid. The goal is to find k representative objects which minimize the sum of the dissimilarities of the objects to their closest representative object. The algorithm first looks for a good initial set of medoids. Then it finds a local minimum for the objective function, that is, a solution such that there is no single switch of an object with a medoid that will decrease the objective.

The k-means algorithm [5], an unsupervised learning algorithm, has been used to form clusters of genes in gene expression data analysis. The algorithm takes the number of clusters (k) to be calculated as an input. The number of clusters is usually chosen by the user. The procedure for k-means clustering is as follows:

- 1. First, the user tries to estimate the number of clusters.

- 2. Randomly choose N points into k clusters.

- 3. Calculate the centroid for each cluster.

- 4. For each point, move it to the closest cluster.

- 5. Repeat steps 3 and 4 until no further points are moved to different clusters.

The Expectation-Maximization (EM) algorithm [6] is a method for finding maximum likelihood estimates of parameters in statistical models, where the model depends on unobserved latent variables. This is a general method for optimizing likelihood functions and is useful in situations where data might be missing or simpler optimization methods fail.

#### B. Unsupervised clustering validation

Clustering validation is a technique to find a set of clusters that best fits natural partitions, *i.e.* number of clusters, without any class information. There are two types of clustering techniques [7], [8]: *external validation*, based on previous knowledge about data and *internal validation*, based on the information intrinsic to the data alone.

There are three external indexes which were used in our previous study [3], Rand index, Jaccard coefficient, and Fowlkes and Mallows index, and they are going to be used also in this paper.

In contrast to external validation, internal validation evaluates the clustering without any a priori information. The obtained values are known as internal indexes as they are computed from the data used for clustering. In this paper we evaluate for the microarray data the following internal indexes: silhouette, Calinski-Harabasz index, Krzanowski-Lai index, Hartigan index and Davies-Bouldin index.

*Silhouette index* calculates the silhouette width for each sample, average silhouette width for each cluster and overall average silhouette width for a total data set:

$$S(i) = \frac{b(i) - a(i)}{\max\{a(i), b(i)\}},$$

(1)

where a(i) is the average dissimilarity of *i*-object to all other objects in the same cluster; b(i) is the minimum of average dissimilarity of *i*-object to all objects in other cluster. The largest overall average silhouette indicates the best clustering.

Calinski-Harabasz index is defined by:

$$CH(k) = \frac{B(k)/(k-1)}{W(k)/(n-k)},$$

(2)

where k denotes the number of clusters, and B(k) and W(k) denote the between and within cluster sums of squares of the partition, respectively. An optimal number of clusters is then defined as a value of k that maximizes CH(k).

Krzanowski-Lai index is given by the equation:

$$KL(k) = \left| \frac{DIFF(k)}{DIFF(k+1)} \right|, \tag{3}$$

where  $DIFF(k) = (k-1)^{2/p}W(k-1) - (k)^{2/p}W(k)$  and *p* denotes the number of features in the data set. A value of *k* is optimal if it maximizes *KL*(*k*).

*Davies-Bouldin index* is a function of the ratio of the sum of within-cluster scatter to between-cluster separation:

$$DB = \frac{1}{n} \sum_{i=1}^{n} \max_{i \neq j} \left\{ \frac{S_n(Q_i) + S_n(Q_j)}{S(Q_i, Q_j)} \right\},\tag{4}$$

where *n* is the number of clusters,  $S_n$  is the average distance of all objects from the cluster to their cluster centre,  $S(Q_i, Q_j)$ is the distance between clusters centres. Consequently, Davies-Bouldin index will have a small value for a good clustering.

For the review, the manuscript is submitted to the IJATES<sup>2</sup> Editorial Board only electronically in PDF format. Do not change any formatting; otherwise you undergo the risk to be directly rejected without review process.

#### C. Gene Shaving

The method of Gene Shaving is designed to extract coherent and typically small clusters of genes that vary as much as possible across the samples. According to [9], the algorithm consists of the following steps:

- 1. Start with the entire expression matrix X, each row centered to have zero mean

- 2. Compute the leading principal component of the rows of *X*

- 3. Shave off the proportion (typically 10 %) of the genes having smallest absolute inner-product with the leading principal component

- 4. Repeat steps 2 and 3 until only one gene remains

- 5. This produces a nested sequence of gene clusters  $S_N \supset S_k \supset S_{k_1} \supset S_{k_2} \supset \cdots \supset S_1$ , where  $S_k$  denotes a cluster of k genes. Estimate the optimal cluster size  $\hat{k}$  using the gap statistic [10].

- 6. Orthogonalize each row of X with respect to  $\bar{x}_{S_k}$ , the average gene in  $S_k$

- 7. Repeat steps 1-5 above with the orthogonalized data, to find the second optimal cluster. This process is continued until a maximum of M clusters are found, where M is chose a priori.

When implementing this method we made some changings compared with the steps form [9]. But I have made some changes in the algorithm. First of all, we shaved off not  $\alpha$  % genes, but 1 gene each time. This is because we will lose the precision of the algorithm if using  $\alpha$ %. For example, supposing we remain with  $S_k$  clusters with k being 135, 122, ..., 53, 47, etc. genes, and according to the gap statistic step, the algorithm decides to have a cluster with 52 or 47 genes, which is not correct. This is the reason why we have decided to have clusters with ..., 53, 52, 51, 50, 49, 48,... genes, in this way hoping to obtain a maximum Gap(k)closer to ideal 50. Also when computing the gap statistics we have made some changes. If we consider all possible permutations and after that finding each D(k), then, in case of 150 genes with 4 characteristics of each gene, it is required to have all possible permutations of the matrix by permuting the elements within each row. This means that each row has from 4 parameters a number of 24 possible permutations, this implies that we have another sets of 24150 matrices, which is too much (we cannot take for example  $3^{rd}$  permutation from gene 1 with  $3^{rd}$  permutation for gene 2,  $3^{rd}$  permutation for gene 3, and so on, because we obtain the same D(k)). We have tried to consider random matrices, a number of 5000, but the problem in this case is that the result is varying at every other analysis and they are also different at each simulation. Finally we have decided to use just the first input matrix and get its D(k) and Gap(k), without any permutations.

#### III. DATA CLUSTERING

#### A. Unsupervised clustering

Three unsupervised algorithms were used to cluster microarray data. We used for our study two different datasets from public Affymetrix databases. The first set was the Chowdary database [11] the authors compared pairs of snap-frozen and RNA later preservative-suspended tissue from 62 lymph node-negative breast tumors and 42 colon tumors, with purpose of separating them. The second set [12] contains 24 acute lymphoblastic leukemia (ALL), 28 acute myelogenous leukemia (AML) and 20 mixed-lineage leukemia (MLL) samples.

For the microarray data the clustering was done by a twoway clustering or bi-clustering [13] in which both the samples and the genes are clustered in the same time using the portioning method.

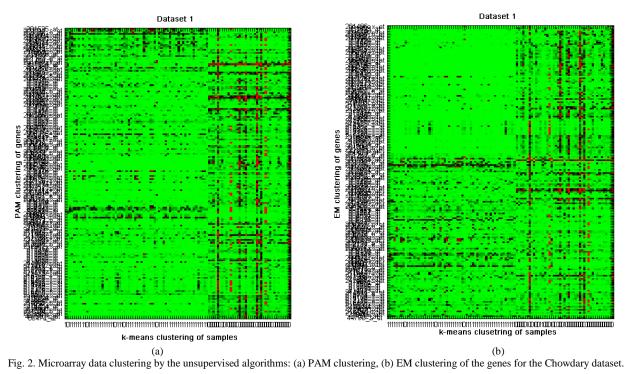

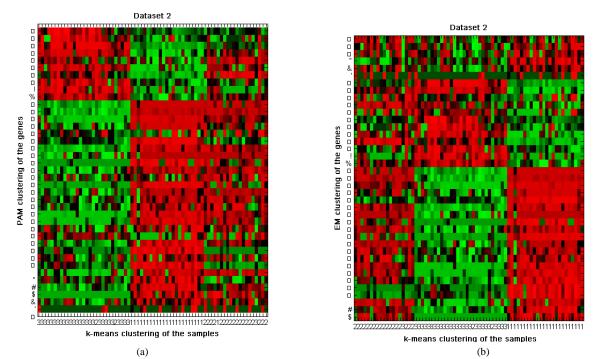

Regarding the conclusions from [3] a useful classification was obtained for microarray data when EM clustered the genes and k-means the samples. In this study we will use the k-means algorithm to cluster the samples and the PAM and respectively the EM algorithm to cluster the genes. Before combining the algorithms we applied the clustering validation methods, both external and internal indexes.

Also, based on these results we combined the unsupervised method with a supervised one. So we clustered the samples by k-means algorithm and we classify the genes using the gene shaving method.

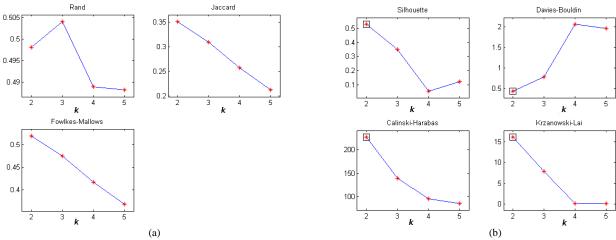

In Table I, the numbers of clusters obtained after using the internal and external indexes are indicated. For the kmeans algorithm the number refers to sample partitioning, while for the PAM and EM algorithms the numbers refers to gene clustering. In the EM clustering validation only the external indexes were computed.

TABLE I THE NUMBER OF CLUSTERS OBTAINED WITH THE CLUSTERING VALIDATION METHODS

|                       | Che   | owdary dat | tabase | Lei   | ıkemia dat | abase |

|-----------------------|-------|------------|--------|-------|------------|-------|

| Index                 | k-    | PAM        | EM     | k-    | PAM        | EM    |

|                       | means |            |        | means |            |       |

| Rand                  | 2     | 3          | 3      | 3     | 3          | 4     |

| Jaccard               | 2     | 2          | 2      | 3     | 3          | 3     |

| Fowlkes-<br>Mallows   | 2     | 2          | 2      | 3     | 3          | 3     |

| Silhouette            | 2     | 2          | -      | 2     | 3          | -     |

| Calinski-<br>Harabasz | 2     | 2          | -      | 3     | 3          | -     |

| Krzanowski<br>-Lai    | 2     | 2          | -      | 3     | 3          | -     |

| Davies-<br>Bouldin    | 2     | 2          | -      | 2     | 3          | -     |

After the validation was done we applied the combined clustering for the datasets. Thereby, for the Chowdary dataset the genes were clustered into 2 groups, with the PAM method, Fig 2.a, and then with the EM algorithm, Fig.2.b. The samples were clustered with the k-means algorithm.

The obtained values were compared with the given values from the microarray databases and a similarity between these values was observed.

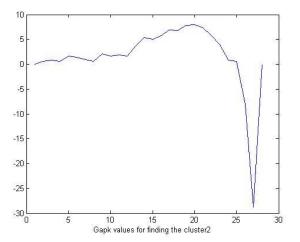

Fig. 1.a and 1.b shows all the computed indexes for the Chowdary database, internal and external, in the case of PAM algorithm. For the external indexes the highest values obtained gave the optimal number of clusters. In the case of internal indexes the optimal value was marked by a square in Fig. 1.b.

According with the optimal number of clusters indicated by the validation indexes, in the case of the leukemia dataset the clustering was done in 3 clusters. Thus the samples were group into three sets by the k-means algorithm, while the genes formed also three groups once with the PAM method

Fig. 3.a Microarray data clustering by the unsupervised algorithms: (a) PAM clustering, (b) EM clustering of the genes for the leukemia dataset.

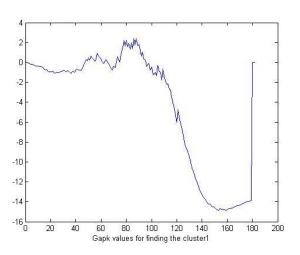

Fig. 4 The values of the Gap(k) function for the Chowdary dataset. The maximum was obtained for a number of 89 genes.

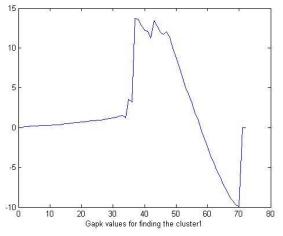

Fig. 5 The values of the Gap(k) function for the leukemia dataset. For the first cluster the maximum was obtained for a number of 37 genes

Fig. 6 The values of the Gap(k) function for the leukemia dataset. For the second cluster the maximum was obtained for a number of 21 genes

and then with the EM algorithm, as it can be seen in Fig. 3.a and Fig. 3.b.

For the gene shaving algorithm we used the same number of clusters as the one given by the validation methods. In the case of Chowdary dataset the genes were classified in 2 sets, while in the case of leukemia dataset we applied gene shaving with 3 clusters.

Once applying the gene shaving method we were able to

classify the Chowdary dataset in 2 clusters. The number of gene in the first cluster was determined by using the gap statistic method. The value of 89 genes was given by the maximum of the graph from Fig. 4.

In a similar manner we computed the gap statistics for the leukemia dataset and we were able to classify the data into 3 clusters: the first one with 37 genes, the second one with 21 genes and the third one with the remaining 14 genes from a total of 72 genes. The values of the Gap function for this dataset are shown in Fig 5 and 6.

#### IV. CONCLUSION

In this paper some unsupervised and supervised clustering methods were applied to microarray dataset in order to obtain a bi-clustering of the data with different algorithms. The selection of the PAM algorithm for clustering the genes, despite of the k-means method was done because of the robustness of the first one. The EM algorithm showed some disadvantages when working with large datasets that is way the data was previously filtered.

Gene shaving, a supervised method was also combined with k-means in order to classify the genes according with the number of clusters given by the validation methods.

For cluster validation we used both internal and external methods by computing some indexes which gave us the optimal number of clusters for each clustering method. As future work we take into consideration the combination of these methods with other data mining algorithms like Independent Component Analysis, which can be used for large datasets.

#### REFERENCES

- S. González, L. Guerra, V. Robles, JM. Peña, F. Famili, "CliDaPa: A new approach to combining clinical data with DNA microarrays" *Intelligent Data Analysis Journal*, vol 14(2), pp. 207 – 223, 2010

- [2] J. Han, M. Kamber, *Data mining: Concepts and techniques*. Morgan Kaufmann, 2000

- [3] R. Malutan, B. Belean, P.G. Vilda, M. Borda, "Two way clustering of microarray data using a hybrid approach" in *Proc. of 34th Int. Conf.* on *Telecommunications and Signal Processing*, Budapest, 2011, pp. 417 - 420

- [4] G. McLachlan, K-A. Do, C. Ambroise, Analyzing Microarray Gene Expression Data. Wiley-Interscience, 2004

- [5] M.B. Zoubi, A. Hudaib, A. Huneiti, B. Hammo, "New efficient strategy to accelerate k-means clustering algorithm" *American Journal of Applied Sciences*, vol 5(9), pp. 1247 – 1250, 2008

- [6] G. McLachlan, T. Krishnan, *The EM Algorithm and Extensions*. John Willey & Sons 2008

- [7] N. Bolshakova, F. Azuaje, "Cluster validation techniques for genome expression data" *Signal Processing* vol 83, pp. 825 – 833, 2002

- [8] K. Wang, B. Wang, L. Peng, "CVAP: Validation for Cluster Analyses" Data Science Journal vol 8, pp. 88 – 93, 2009

- [9] T. Hastie *et. al.*, "Gene shaving as a method for identifying distinct sets of genes with similar expression patterns", *Genome Biology*, vol. I(2), research 0003, pp. 1-21, 2000

- [10] W. L. Martinez, A. R. Martinez, Exploratory Data Analysis with MATLAB, CRC Press LLC, 2005

- [11] D. Chowdary *et al*, "Prognostic gene expression signatures can be measured in tissues collected in RNAlater preservative" *J Mol Diagn* vol 8(1), pp. 31 – 39, 2006

- [12] S. Armstrong *et al*, "MLL translocations specify a distinct gene expression profile that distinguishes a unique leukemia" *Nature Genetics* vol 30, pp. 41 – 47, 2001

- [13] S. C. Madeira, A. L. Oliveira, "Biclustering algorithms for biological data analysis: A survey" *IEEE/ACM Transactions on Computational Biology and Bioinformatics* vol 1 (1), pp. 24-45, 2004

### Neural Networks Based Physical Cell Identity Assignment for Self Organized 3GPP Long Term Evolution

M. Basit Shahab and Abdul Aziz Bhatti

*Abstract*— This paper proposes neural networks based graph coloring technique to assign Physical Cell Identities throughout the self-organized 3GPP Long Term Evolution Networks. PCIs are allocated such that no two cells in the vicinity of each other or with a common neighbor get the same identity. Efficiency of proposed methodology resides in the fact that minimum number of identities is utilized in the network wise assignment. Simulations are performed on a very large scale network, where initially all the cells are without any PCIs assigned. Results of simulations are demonstrated to analyze the performance of the proposed technique. Discussions about the presence of femto cells and PCI assignment in them are also presented at the end.

*Keywords*— Collision, Confusion, Graph Coloring, Long Term Evolution, Neural Networks, Physical Cell Identity (PCI)

#### I. INTRODUCTION

With an increase in the number of mobile users utilizing cellular networks and thus the wireless technology, demands on systems and their management have increased up to a very high level. Auto configuration, optimization and healing of radio parameters using self-organized networks [1], is a key feature in meeting the requirements of the future mobile cellular networks. Therefore the New Generation Mobile Networks Forum [2] has listed some key parameters that should be handled by adaptive algorithms. 3GPP Long Term Evolution, referred to as LTE and marketed as 4G LTE. is a standard for wireless communication for mobile phones and data terminals. It aims at high data rates [3][4], low delay/latency, high spectral efficiency, high performance broadcast services, cost effective network design, automatic neighbor relation, coverage and capacity optimization, energy saving, interference reduction, physical cell identity automatic configuration, mobility load balancing optimization and random access channel optimization. These goals result in reducing capital expenditures (CAPEX) and operational expenditures (OPEX), by replacing most of the manual work with adaptive techniques that auto tune the network according to the environment changes. One of these parameters is the PCI.

Abdul Aziz Bhatti (PhD) is the Dean of School of Science and Technology, University of Management and Technology, Lahore, Pakistan (Phone: +92-305-4440629; Email: drabhatti@umt.edu.pk).

#### II. PREVIOUS WORK

In LTE, each base station named eNodeB broadcasts a distinguishing signal, a fingerprint that helps the user equipment to differentiate between the serving and the neighboring cells [5]. In some circumstances, a conflict occurs among the PCIs of neighboring cells, which results in handover failures when the user equipment being mobile, moves across the boundaries of these regions. This is due to the fact that mobile units can't differentiate between two same broadcasted PCI's, irrespective of their signal strengths. A solution to this problem needs to be explored based on Neighbor cell relation lists [6][7], in order to improve the efficiency of future networks, in the sense that they will have a lesser number of call drops, better quality, improved coverage and efficient mobility handling.

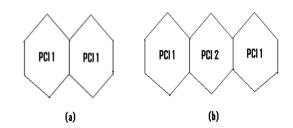

Various types of cases in the PCI assignment issue have been explored [8], according to which it is quite clear that two types of conflicts can occur while assigning the PCIs in a cellular network; when two cells in the vicinity of each other or two cells having a common neighbor are assigned the same PCI. This causes collision in the former, and confusion in the later case. The situations are depicted in Figure 1.

Figure 1: (a) Collision, (b) Confusion

In the first case; Figure 1 (a), two adjacent cells have the same PCI. When user equipment in either of these two cells moves across the cell boundary towards the adjacent cell with same PCI, a collision is detected and may result in handover failure. In the second case Figure 1 (b), two outer cells having the central cell as a common neighbour have same PCI, resulting in a confusion kind of conflict, which causes handover failure during mobility from either one of them towards the central cell. In order to improvise mobility handling quality throughout the cellular network, these conflicts must be resolved.

M. Basit Shahab is a Lecturer at Electrical Engineering Department, University of Management and Technology, Lahore, Pakistan (Phone: +92-333-9299532; Email: basit.shahab@umt.edu.pk).

#### **III. RELATED WORK**

Numerous techniques and algorithms have been proposed to solve these conflicts. Graph coloring is considered as a better approach. In this technique, each cell is considered as a vertex of a graph, and all the cells which are direct neighbours to each other, represented by these vertices are connected through an edge. Trick towards solution is to assign colours to the vertices in such a way, that both cases are properly handled. Solution to Figure 1(a), and 1(b), has been demonstrated in Figure 2(a) and Figure 2(b).

Figure 2: (a) Collision free assignment, (b) Confusion free assignment

So far, various graph coloring techniques and methods of graph coloring optimization have been proposed [9] [10] [11]. Graph coloring is used in many applications like VLSI Channel Routing [12], Subcarrier allocation in Cognitive Radio [13], and has been implemented using neural networks [14]. Any graph coloring technique can be applied to solve the PCI assignment task, but the major goal is to resolve the conflicts using minimum number of colours/PCIs. One method, dealing with a four-color-map problem is explored [15], followed by graph coloring using neural networks [16]. A neural network parallel algorithm for channel assignment problems in cellular radio networks is a step that utilizes neural networks in the telecommunication area [17].

#### IV. MATHEMATICAL MODELLING

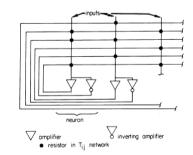

Consider a case of "n" cells in a cellular network and "m" available PCIs or colours to be assigned to these cells with no collision or confusion conflicts. The very famous Hopfield neuron model is considered as shown in Figure 3. Two types of amplifiers are involved in the circuit. An ordinary amplifier and its inverting version are present. Impulse is the input applied to neurons. Feedback paths are also shown. Output is passed through the sigmoid function to determine whether it is 0 or 1.

Figure 3: Hopfield neuron model

Three restrictions are applied on the Hopfield network.

- 1) Inputs and outputs are binary (exclusively ones or zeros). Considering this, it should be quite clear that the nodes produce only binary results.

- 2) There should be no weights.

3) A condition on the activation function applied such that it is always a unit step.

This model is also applied in artificial neural networks for four-coloring problems and k colorability [18], an NP complete problem [19], in which colors are assigned to different regions in a map, so that no two regions having a common boundary should get the same color. In four-coloring problem and k colorability, after all the mathematical work involved, final energy equation for an i<sup>th</sup> neuron in any X<sup>th</sup> region is

$$E = \frac{A}{2} \sum_{x=1}^{n} \left[ \sum_{i=1}^{m} V_{xi} - 1 \right]^{2} + B \sum_{x=1}^{n} \sum_{y=1}^{n} \sum_{i=1}^{m} D_{xy} V_{xi} V_{yi}$$

(1)

Where

The first term makes sure that only one neuron's output is 1 in each region. This is done due to the fact that each neurons output corresponds to a particular color. If multiple neurons' outputs are 1 in a particular region, then more than one color will be allocated to this region, which is to be avoided. The second term makes sure that no two adjacent/ neighboring cells get the same color. For any two regions X and Y, the adjacency matrix Dxy describes the adjacency between these two regions. If X and Y are direct neighbors to each other, then the value corresponding to their relationship will be 1 in the matrix Dxy. Thus for this case, if the values of Vxi and Vyi are same which means that both neurons have the same output, there will be an energy penalty equal to the value of the constant B. As this equation always tries to converge to the 0 energy point, therefore, such condition will be avoided. In short, this second term makes sure that the color allocation is collision free.

This is followed by motion equation, which is actually the partial derivative of (1) with respect to neuron's output.

$$\frac{dU_{xi}}{dt} = -A[\sum_{i=1}^{m} V_{xi} - 1] - B\sum_{Y=1}^{n} D_{xy} V_{yi} \sum_{k=1}^{n} D_{yk} + C.h(\sum_{i=1}^{m} V_{xi}) \left(C1\sum_{k=1}^{n} D_{xk} + C2\frac{\sum_{k=1}^{n} \sum_{Y=1}^{n} D_{xy} D_{yk}}{\sum_{k=1}^{n} D_{xk}}\right)$$

(2)

Colors to the map are allocated by applying sigmoid function on the final motion equation.

$$Sig \begin{pmatrix} -A[\sum_{i=1}^{m} V_{xi} - 1] - B \sum_{Y=1}^{n} D_{xy} V_{yi} \sum_{k=1}^{n} D_{yk} \\ + C.h(\sum_{i=1}^{m} V_{xi}) \\ \left( C1 \sum_{k=1}^{n} D_{xk} + C2 \frac{\sum_{k=1}^{n} \sum_{Y=1}^{n} D_{xy} D_{yk}}{\sum_{k=1}^{n} D_{xk}} \right) \end{pmatrix}$$

(3)

This equation is written for the map coloring case, but it can also be used in solving collision free PCI assignment problem. Second case that remains unsolved is the confusion free assignment. This paper extends Yoshiyasu Takefuji's neural networks k-colorability map coloring approach in the form of a single equation for both collision free and the unresolved confusion free PCI assignment. One important factor that needs to be taken care of simultaneously is the upper and lower bounds on chromatic number, which in the other sense means an assignment with minimum number of PCIs utilized.

The proposed technique starts with writing an energy equation like (3) for some i<sup>th</sup> PCI in an  $X^{th}$  cell. The first thing to be kept in mind is that only one neuron's output should be 1 in any cell, otherwise more than one colors/PCIs will be assigned to a single cell. For that reason, one term in the energy equation, same as the term proposed for collision free assignment, should be present, to deal with the issue. This has been done in (4).

$$E1 = \frac{A}{2} \sum_{x=1}^{n} [\sum_{i=1}^{m} V_{xi} - 1]^2, \qquad (4)$$

where A is a constant, used to represent an energy penalty.  $V_{xi}$  is the output of i<sup>th</sup> neuron in X<sup>th</sup> cell. Second term needs to deal with the case of collision and confusion free assignment, as depicted in (5).

$$E2 = B \sum_{X=1}^{n} \left[ \sum_{Y=1}^{n} \sum_{Z=1}^{n} \sum_{i=1}^{m} D_{xy} D_{xz} V_{xi} V_{yi} V_{zi} \right], \quad (5)$$

where B is a constant that will take the energy away from converging, if a boundary violation takes place.  $D_{xy}$  and  $D_{xz}$  are elements of the adjacency matrices between X, Y, and X, Z.  $V_{xi}$ ,  $V_{yi}$  and  $V_{zi}$  are outputs of the i<sup>th</sup> neuron in X<sup>th</sup>, Y<sup>th</sup> and Z<sup>th</sup> cell respectively.

$$\begin{split} D_{ij} = \{1 \text{ if any region } i \text{ and } j \text{ are adjacent} \\ \{0 \text{ otherwise} \end{split}$$

(4) And (5) together result in (6)

$$E = \frac{A}{2} \sum_{X=1}^{n} [\sum_{i=1}^{m} V_{xi} - 1]^{2} + B \sum_{X=1}^{n} [\sum_{Y=1}^{n} \sum_{Z=1}^{n} \sum_{i=1}^{m} D_{xy} D_{xz} V_{xi} V_{yi} V_{zi}]$$

(6)

Motion equation for an i<sup>th</sup> PCI in any X<sup>th</sup> cell is the partial derivative of Energy equation with respect to neuron's output

$$\frac{dU_{xi}}{dt} = -\frac{\partial E}{\partial V_{xi}} \tag{7}$$

Because interest lies in the output of some  $i^{th}$  neuron in any  $X^{th}$  Cell, applying partial derivative on the energy equation with respect to  $V_{xi}$ , results in equation (8).

$$\frac{dU_{xi}}{dt} = -\frac{\partial}{\partial V_{xi}} \left[ \frac{A}{2} \sum_{X=1}^{n} \left[ \sum_{i=1}^{m} V_{xi} - 1 \right]^{2} \right] - \frac{\partial}{\partial V_{xi}} B \sum_{X=1}^{n} \left[ \sum_{Y=1}^{n} \sum_{Z=1}^{n} \sum_{i=1}^{m} D_{xy} D_{xz} V_{xi} V_{yi} V_{zi} \right]$$

(8)

Expanding the 1<sup>st</sup> term i-e E1 with respect to X and taking the partial derivative for some specific value, gives

$$\frac{\partial E_1}{\partial V_{xi}} = A[\sum_{i=1}^m V_{xi} - 1] \tag{9}$$

Writing (5) in terms of X and i, gives

$$\frac{\partial E^2}{\partial V_{xi}} = B \frac{\partial}{\partial V_{xi}} \left[ \left[ \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{1y} D_{1z} V_{11} V_{y1} V_{z1} \right] + \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{1y} D_{1z} V_{12} V_{y2} V_{z2} \right] + \\ \dots \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{1y} D_{1z} V_{1m} V_{ym} V_{zm} \right] \right] + \\ \left[ \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{2y} D_{2z} V_{21} V_{y1} V_{z1} \right] + \\ \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{2y} D_{2z} V_{22} V_{y2} V_{z2} \right] + \\ \dots \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{2y} D_{2z} V_{2m} V_{ym} V_{zm} \right] \right] + \\ \left[ \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{2y} D_{3z} V_{31} V_{y1} V_{z1} \right] + \\ \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{3y} D_{3z} V_{32} V_{y2} V_{z2} \right] + \\ \dots \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{3y} D_{3z} V_{3m} V_{ym} V_{zm} \right] \right] + \\ \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{ny} D_{nz} V_{n1} V_{y1} V_{z1} \right] + \\ \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{ny} D_{nz} V_{n2} V_{y2} V_{z2} \right] + \\ \dots \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{ny} D_{nz} V_{n2} V_{y2} V_{z2} \right] + \\ \dots \left[ \sum_{Y=1}^n \sum_{Z=1}^n D_{ny} D_{nz} V_{nm} V_{ym} V_{zm} \right] \right] \right]$$

(10)

Partial derivative is applied for some specific X and i, but in general, (10) becomes

$$\frac{\partial E2}{\partial V_{xi}} = B\left[\sum_{Y=1}^{n} \sum_{Z=1}^{n} D_{xy} D_{xz} V_{yi} V_{zi}\right]$$

(11)

Combining (9) and (11), gives the motion equation

$$\frac{\partial E}{\partial V_{xi}} = A[\sum_{i=1}^{m} V_{xi} - 1] + B[\sum_{Y=1}^{n} \sum_{Z=1}^{n} D_{xy} D_{xz} V_{yi} V_{zi}]$$

(12)

But

$$\frac{dU_{xi}}{dt} = -\frac{\partial E}{\partial V_{xi}}$$

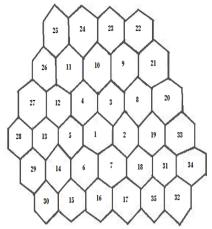

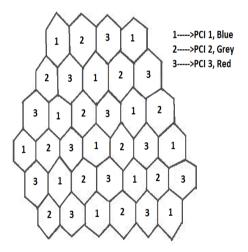

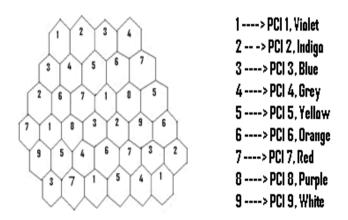

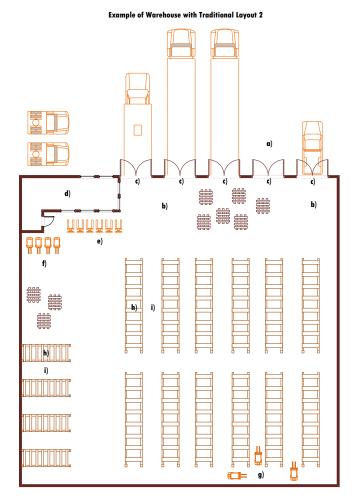

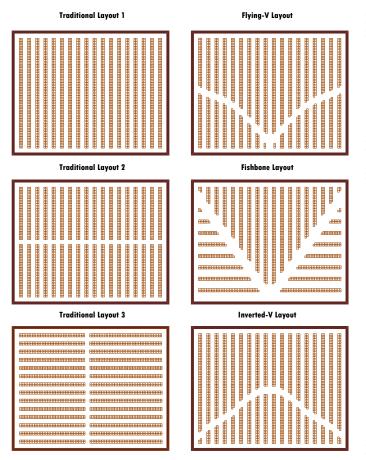

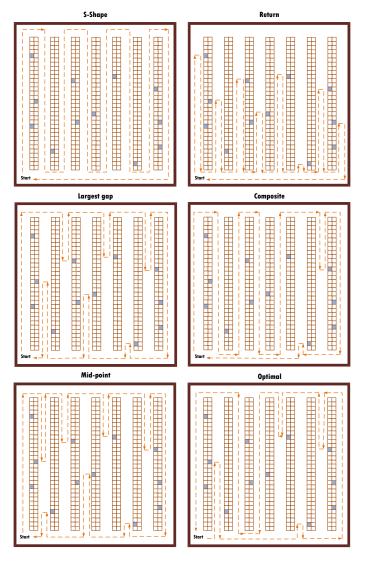

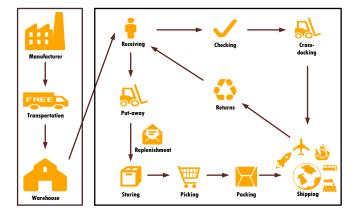

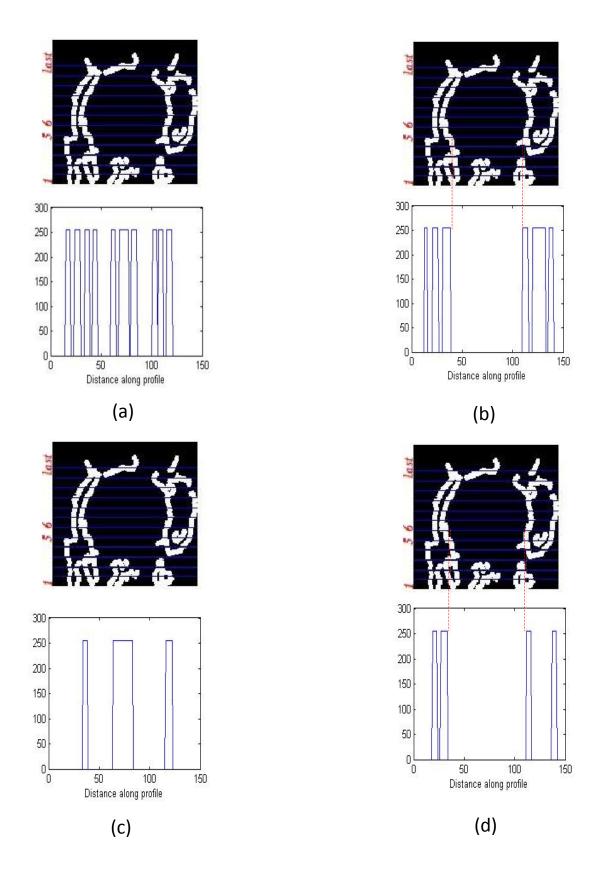

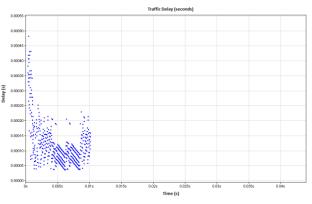

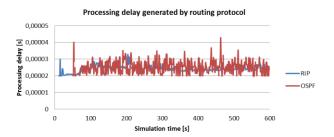

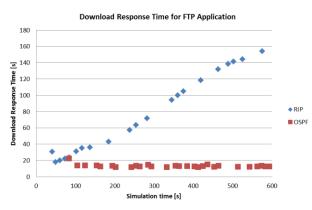

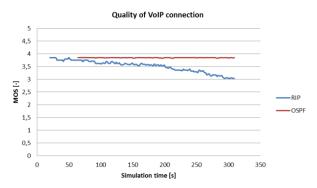

, so